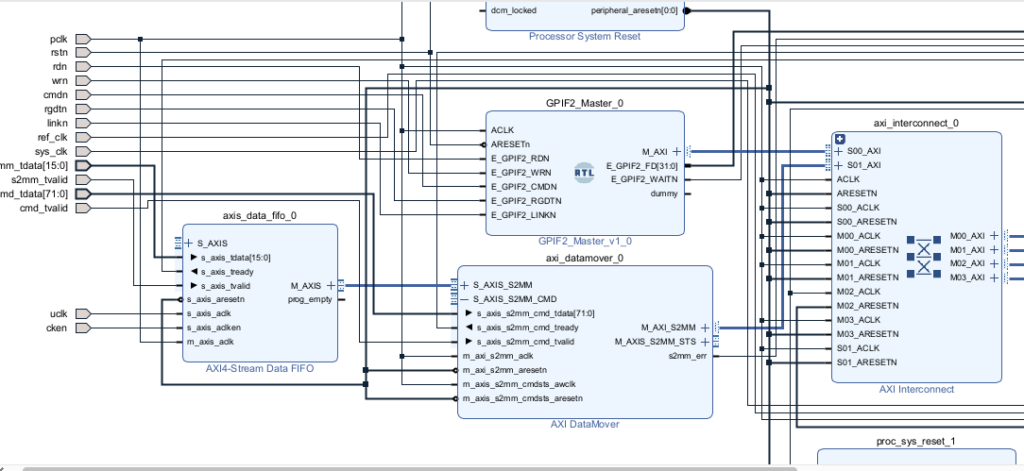

AXIバスマスタのGPIF2_Master IPを利用して、ADデータなどの外部データをBRAMやDDR3に取り込むには、AXI Data Mover IPやAXI Stream Data FIFO IPを利用することで、グルーロジックなしに処理できます。

AXI Data Mover IP

AXI StreamプロトコルをAXI Memroy Mapに変換します。つまり、バスマスタ「GPIF2_Master」を利用したAXIバスシステムにこのIPを接続することで、DMAを利用せずにAXI Streamで収集したデータを内部メモリ(BRAM)やDDR3メモリに自動的に転送します。 AXI DataMover IPには、転送先のベースアドレスと転送量の指定を設定し、データ転送に先立ってコマンドを発行する必要があります。

vivado block designツール上では、axi_datamoverブロックのM_AXI_S2MMポートをaxi_interconnetブロックのスレーブポートに接続するだけです。

データを収集する側のaxi_datamoverブロック S_AXI_S2MMポートは、次に示すAXI Stream DATA FIFO IPに接続します。

AXI Stream DATA FIFO IP

AXI DataMover IPは100MHzのAXIバスに接続しているので、AXI Stream DATA FIFO IPも100MHzのAXIクロックとデータ収集用のユーザクロックに設定します(Independent clocks=Yes)。収集するデータのビット幅はAXI DataMover IP(最大ビット幅=1024)と共通にします。共通にしない、またはできない場合は、AXI Stream Data Width Converter IPを経由してAXI Data Mover IPと接続できます。 FIFOへの書き込みは、Stream DATA FIFO IPのユーザクロックを制御するs_axis_aclken信号でon/offできます。

サンプルプロジェクト

AX-Card7システム開発ボード用:約104MB、vivado2023.1使用

【内 容】

FPGAに実装したデバッグ用のバイナリカウンタ出力(16bit)を4MB分、DDR3に転送します。DDR3のデータはUSBでバイナリファイル化できます。動作確認には、C#サンプルのRefApp8リファレンス制御アプリを使用してください。

デバッグ用のカウンタ部分をカスタマイズすれば、外部データを簡単にDDR3に収集できます。周期的にAD変換するようなシステムなら、ADコンバータとのIFだけ設計すればプロジェクトが完成します。

【動作確認方法】

1.RefApp8を起動後、\bin_100フォルダの”axcard7axi.bin”をコンフィグ。

2.「レジスタ操作」タブの設定

レジスタ番号(2,097,151)に、0x5000_0000(AXIバスレジスタのGPIOベースアドレス)をWR。

レジスタ番号(2,097,150)に、0x8000_0000(AXIバスレジスタのDDR3ベースアドレス)をWR。

レジスタ番号(0)に、0x1をWR。ボードのLEDが一瞬点灯します。その後0x0をWR。

3.「レジスタ操作」タブで、0x40_0000バイトRDすると、サンプル回路中のデバッグカウンタ値が読み出せます。